NVSwitch芯片周圍MLCC陣列的PDN阻抗優化方案

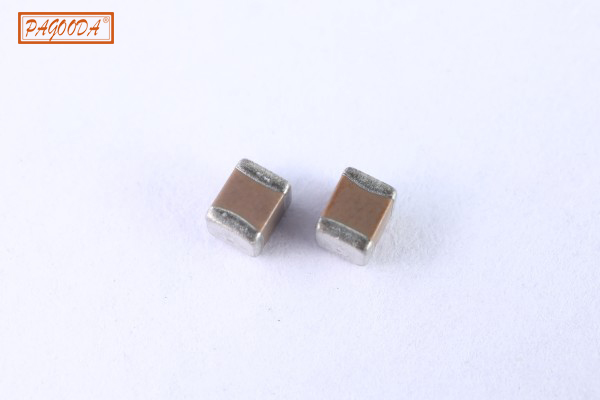

在AI計算集群高速發展的今天,NVSwitch芯片作為實現多GPU互聯的核心器件,其供電網絡(PDN)的阻抗特性直接影響著信號傳輸質量和系統穩定性。MLCC(多層陶瓷電容)陣列在PDN阻抗優化中扮演著關鍵角色,東莞市平尚電子科技有限公司基于工業級技術積累,為AI加速計算系統提供了可靠的MLCC解決方案。

PDN阻抗的頻域特性要求MLCC陣列具備全頻段覆蓋能力。平尚科技的MLCC采用X7R介質材料,在100kHz至10MHz的中頻段,等效串聯電阻(ESR)可穩定在0.8mΩ以下,配合低電感封裝設計,將等效串聯電感(ESL)控制在0.2nH以內。與普通MLCC相比,這種優化使得在NVSwitch芯片的供電端口處,目標阻抗可降低至1.5mΩ以下,有效抑制芯片工作時的電壓波動。

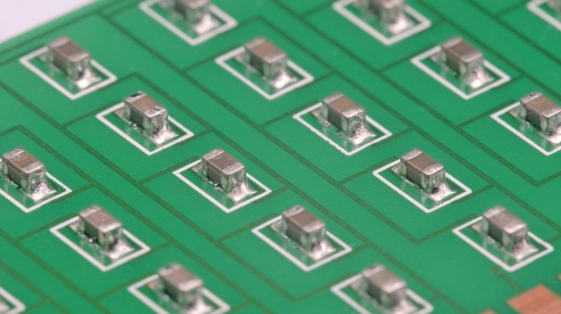

電容值的選擇需要根據芯片的電流特性精確配置。平尚科技通過建立精確的仿真模型,建議在NVSwitch芯片周圍采用多值并聯的方案:100nF電容負責抑制高頻噪聲,10μF電容處理中頻段的電流需求,再輔以47μF電容應對低頻波動。這種組合相比單一容值的方案,可將電壓紋波峰值控制在15mV以內,優于普通設計的25mV水平。

溫度穩定性對MLCC的高頻特性具有重要影響。平尚科技的MLCC通過優化介質材料和電極結構,在-55℃至125℃溫度范圍內,容量變化率控制在±7%以內。相比之下,普通Y5V材料的MLCC在相同條件下的容量變化可能超過±30%。這種穩定性確保了在AI訓練服務器長時間高負載運行時,PDN阻抗特性不會因溫度波動而發生顯著變化。

封裝尺寸的選擇需要平衡性能與空間限制。平尚科技的0201封裝MLCC通過改進端電極設計,在保持0.1μF容量的同時,寄生電感降至0.15nH,比0402封裝的0.3nH降低約50%。這種特性在NVSwitch芯片周圍的密集布局中尤為重要,可以有效減少去耦半徑,提升高頻響應速度。

在實際應用案例中,平尚科技的MLCC陣列方案已成功應用于多個AI計算項目。在某國產AI服務器的NVSwitch供電系統中,采用優化設計的MLCC陣列,將電源完整性(PI)的均方根噪聲控制在8mV以內,同時實現了在100MHz頻率范圍內低于2mΩ的目標阻抗。這些參數完全滿足國內AI硬件廠商對高速互連系統的供電要求。

布局策略對阻抗優化效果的影響同樣關鍵。平尚科技建議采用"先小后大"的布局原則,將小容量MLCC盡可能靠近芯片電源引腳,大容量電容適當外擴。通過合理的布局設計,可以有效降低PDN的環路電感,將高頻段的阻抗峰值抑制在5mΩ以下。

焊接可靠性是確保MLCC性能充分發揮的基礎。平尚科技的MLCC通過采用柔性端電極結構,在溫度循環測試中,可承受-55℃至125℃的1000次循環而無開裂現象。這種機械穩定性確保了在服務器長期運行過程中,MLCC陣列能夠保持穩定的電氣性能。

平尚科技工業級MLCC產品已通過嚴格的可靠性驗證。在85℃/85%RH的高溫高濕測試中,絕緣電阻保持在10^8Ω以上,且容量變化率不超過初始值的±5%,完全滿足AI加速計算系統對元器件可靠性的要求。

隨著AI計算芯片功耗的不斷提升,PDN阻抗優化將面臨更大挑戰。平尚科技通過持續改進MLCC的介質材料和封裝技術,為NVSwitch等高速芯片提供了可靠的供電保障,助力國產AI計算系統實現更高水平的性能表現。